# DESIGN AND IMPLEMENTATION OF HIGH FREQUENCY SIGNAL GENERATOR BASED ON PHASE LOCKED LOOP

MUTINDA BONIFACE MUSYOKA (B.Ed. Sci)

156/20697/2020

A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE AWARD OF DEGREE OF MASTER OF SCIENCE (ELECTRONICS AND INSTRUMENTATION) IN THE SCHOOL OF PURE AND APPLIED SCIENCES OF KENYATTA UNIVERSITY

NOVEMBER 2023

## DECLARATION

This thesis is my original work and has not been presented for degree or other awards in any other university.

Signature.....Date....

Boniface Mutinda

Department of Physics

Kenyatta University

# **SUPERVISORS**

We confirm that the work reported in this thesis was carried out by the candidate under our supervision.

Signature.....Date....

Dr. Mathew Munji

Department of Physics

Kenyatta University

Signature.....Date.....

Dr. Raphael Nyenge

Department of Physics

Kenyatta University

# DEDICATION

To my parents, Isaac Mutinda and Mary Mueni, and siblings, Judith Kithia, Elizabeth Mwikali, Emmaculate Nzisa and Antony Muema.

#### ACKNOWLEDGMENTS

I would like to take this opportunity to thank my supervisors, Dr. Mathew Munji and Dr. Raphael Nyenge, for all of the assistance and support they provided me while I was conducting my research. You have been a great source of knowledge for me; without you, I would never have been able to get to this point. I would also like to take this opportunity to thank the staff and academic members of the Department of Physics at Kenyatta University for the assistance they provided and the words of encouragement they offered.

I want to appreciate the Kenyatta University Electrical Engineering Department chairman and staff for allowing me to carry out measurements using a spectrum analyser in the Electronics lab.

I'd like to take this opportunity to thank my comrades Marcelina Kinyumu, Paul Angira, Daniel Ndengwa, and Mary Ndimuwaki for their humble time and the positive atmosphere of sharing knowledge and helping one another. It's been a pleasure working with you guys.

I would like to take this opportunity to convey my appreciation to my entire family, and in particular to my parents, for their unflinching support and encouragement throughout this entire process of my research. You have modeled the man I am today, and I cannot thank you enough. I also want to thank all my friends who have always been there for me in times of hardship.

In conclusion, I would like to express my gratitude to the Almighty God for the unwavering support and guidance that He has provided throughout my life.

# **TABLE OF CONTENTS**

| DI | ECLA                               | RATION                                           | ii  |  |  |  |  |

|----|------------------------------------|--------------------------------------------------|-----|--|--|--|--|

| DI | EDIC                               | ATION                                            | iii |  |  |  |  |

| AC | CKNO                               | OWLEDGMENTS                                      | iv  |  |  |  |  |

| TA | BLE                                | OF CONTENTS                                      | v   |  |  |  |  |

| LI | ST O                               | F FIGURES                                        | ix  |  |  |  |  |

| LI | ST O                               | F TABLES                                         | xi  |  |  |  |  |

| LI | ST O                               | F ABBREVIATIONS AND ACRONYMS                     | xii |  |  |  |  |

| AI | BSTR                               | ACT                                              | XV  |  |  |  |  |

| 1  | -                                  | APTER ONE<br>RODUCTION                           | 1   |  |  |  |  |

|    | 1.1                                | Background of the Study                          | 1   |  |  |  |  |

|    | 1.2                                | Statement of the Problem                         | 4   |  |  |  |  |

|    | 1.3                                | Justification of the Study                       | 4   |  |  |  |  |

|    | 1.4                                | Objectives                                       | 5   |  |  |  |  |

|    |                                    | 1.4.1 General Objective                          | 5   |  |  |  |  |

|    |                                    | 1.4.2 Specific Objectives                        | 5   |  |  |  |  |

|    | 1.5                                | Significance of the Study                        | 5   |  |  |  |  |

| 2  | CHAPTER TWO<br>LITERATURE REVIEW 6 |                                                  |     |  |  |  |  |

|    | 2.1                                | Introduction                                     | 6   |  |  |  |  |

|    | 2.2                                | Direct Digital Synthesis based Signal Generators | 6   |  |  |  |  |

|    | 2.3                                | Phase Locked Loop Generators                     | 7   |  |  |  |  |

|    | 2.4                                | Simulation of PLL                                | 8   |  |  |  |  |

| 3  | -                                  | APTER THREE<br>EORETICAL BACKGROUND              | 10  |  |  |  |  |

|    | 3.1                                | Introduction                                     | 10  |  |  |  |  |

|    | 3.2                                | Components of a Phase Locked Loop                | 10  |  |  |  |  |

|    |                                    | 3.2.1 Reference Crystal Oscillator               | 10  |  |  |  |  |

|   |            | 3.2.2                                                                   | Phase / Frequency Detector (PFD)                                                                                                                                                                                                                                                                                                                                                             | 11                                                                                                                                                                     |

|---|------------|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |            | 3.2.3                                                                   | Charge Pump                                                                                                                                                                                                                                                                                                                                                                                  | 12                                                                                                                                                                     |

|   |            | 3.2.4                                                                   | Loop Filter                                                                                                                                                                                                                                                                                                                                                                                  | 13                                                                                                                                                                     |

|   |            | 3.2.5                                                                   | Voltage Controlled Oscillator                                                                                                                                                                                                                                                                                                                                                                | 15                                                                                                                                                                     |

|   |            | 3.2.6                                                                   | Programmable Frequency Divider                                                                                                                                                                                                                                                                                                                                                               | 17                                                                                                                                                                     |

|   | 3.3        | Fractio                                                                 | nal-N Phase Locked Loop                                                                                                                                                                                                                                                                                                                                                                      | 19                                                                                                                                                                     |

|   |            | 3.3.1                                                                   | Delta Sigma ( $\Sigma$ - $\Delta$ ) Modulators in Fractional Phase Locked Loop                                                                                                                                                                                                                                                                                                               | 21                                                                                                                                                                     |

|   | 3.4        | Phase I                                                                 | Noise                                                                                                                                                                                                                                                                                                                                                                                        | 22                                                                                                                                                                     |

|   |            | 3.4.1                                                                   | Phase Noise Modeling of Phase-Locked-Loop                                                                                                                                                                                                                                                                                                                                                    | 22                                                                                                                                                                     |

|   | 3.5        | Phase-                                                                  | Locked-Loop Spurs                                                                                                                                                                                                                                                                                                                                                                            | 25                                                                                                                                                                     |

|   |            | 3.5.1                                                                   | Reference Spurs                                                                                                                                                                                                                                                                                                                                                                              | 25                                                                                                                                                                     |

|   |            | 3.5.2                                                                   | Fractional Spurs                                                                                                                                                                                                                                                                                                                                                                             | 25                                                                                                                                                                     |

|   |            | 3.5.3                                                                   | Crosstalk spurs                                                                                                                                                                                                                                                                                                                                                                              | 26                                                                                                                                                                     |

|   | 3.6        | Voltage                                                                 | e Regulators                                                                                                                                                                                                                                                                                                                                                                                 | 26                                                                                                                                                                     |

|   |            | 3.6.1                                                                   | Linear Regulators                                                                                                                                                                                                                                                                                                                                                                            | 26                                                                                                                                                                     |

| 4 | СН         | DTFD                                                                    | FOUR                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                        |

| - |            | APTER FOUR<br>TERIALS AND METHODS 29                                    |                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                        |

|   |            |                                                                         |                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                        |

|   | 4.1        | Introdu                                                                 | ction                                                                                                                                                                                                                                                                                                                                                                                        | 29                                                                                                                                                                     |

|   | 4.1<br>4.2 |                                                                         | Iction                                                                                                                                                                                                                                                                                                                                                                                       | 29<br>29                                                                                                                                                               |

|   |            |                                                                         |                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                        |

|   |            | System                                                                  | Design                                                                                                                                                                                                                                                                                                                                                                                       | 29                                                                                                                                                                     |

|   |            | System<br>4.2.1                                                         | Design                                                                                                                                                                                                                                                                                                                                                                                       | 29<br>29                                                                                                                                                               |

|   |            | System<br>4.2.1<br>4.2.2                                                | Design                                                                                                                                                                                                                                                                                                                                                                                       | 29<br>29<br>30                                                                                                                                                         |

|   |            | System<br>4.2.1<br>4.2.2                                                | Design                                                                                                                                                                                                                                                                                                                                                                                       | 29<br>29<br>30<br>31                                                                                                                                                   |

|   |            | System<br>4.2.1<br>4.2.2                                                | Design                                                                                                                                                                                                                                                                                                                                                                                       | 29<br>29<br>30<br>31<br>32                                                                                                                                             |

|   |            | System<br>4.2.1<br>4.2.2                                                | Design                                                                                                                                                                                                                                                                                                                                                                                       | <ol> <li>29</li> <li>29</li> <li>30</li> <li>31</li> <li>32</li> <li>33</li> </ol>                                                                                     |

|   |            | System<br>4.2.1<br>4.2.2                                                | Design                                                                                                                                                                                                                                                                                                                                                                                       | <ol> <li>29</li> <li>29</li> <li>30</li> <li>31</li> <li>32</li> <li>33</li> <li>34</li> </ol>                                                                         |

|   |            | System<br>4.2.1<br>4.2.2                                                | Design                                                                                                                                                                                                                                                                                                                                                                                       | <ol> <li>29</li> <li>29</li> <li>30</li> <li>31</li> <li>32</li> <li>33</li> <li>34</li> <li>35</li> </ol>                                                             |

|   |            | System<br>4.2.1<br>4.2.2                                                | Design                                                                                                                                                                                                                                                                                                                                                                                       | <ol> <li>29</li> <li>29</li> <li>30</li> <li>31</li> <li>32</li> <li>33</li> <li>34</li> <li>35</li> <li>36</li> </ol>                                                 |

|   |            | System<br>4.2.1<br>4.2.2<br>4.2.3                                       | DesignThe Signal Generator SpecificationsSimulation Tool usedPhase-Locked-Loop Chip4.2.3.1Reference Input Section4.2.3.2ADF4351 Dividers4.2.3.3Multiplexer Output4.2.3.4Input Shift Registers in ADF43514.2.3.5Voltage Controlled Oscillator integrated in ADF43514.2.3.6Output Stage of the ADF4351                                                                                         | <ol> <li>29</li> <li>29</li> <li>30</li> <li>31</li> <li>32</li> <li>33</li> <li>34</li> <li>35</li> <li>36</li> <li>37</li> </ol>                                     |

|   |            | System<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.4<br>4.2.5            | DesignThe Signal Generator SpecificationsSimulation Tool usedPhase-Locked-Loop Chip4.2.3.1Reference Input Section4.2.3.2ADF4351 Dividers4.2.3.3Multiplexer Output4.2.3.4Input Shift Registers in ADF43514.2.3.5Voltage Controlled Oscillator integrated in ADF43514.2.3.6Output Stage of the ADF4351Loop Filter                                                                              | <ol> <li>29</li> <li>29</li> <li>30</li> <li>31</li> <li>32</li> <li>33</li> <li>34</li> <li>35</li> <li>36</li> <li>37</li> <li>38</li> </ol>                         |

|   | 4.2        | System<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.4<br>4.2.5            | Design                                                                                                                                                                                                                                                                                                                                                                                       | <ol> <li>29</li> <li>29</li> <li>30</li> <li>31</li> <li>32</li> <li>33</li> <li>34</li> <li>35</li> <li>36</li> <li>37</li> <li>38</li> <li>39</li> </ol>             |

|   | 4.2        | System<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.3<br>4.2.4<br>4.2.5<br>Buildir | DesignThe Signal Generator SpecificationsSimulation Tool usedPhase-Locked-Loop Chip4.2.3.1Reference Input Section4.2.3.2ADF4351 Dividers4.2.3.3Multiplexer Output4.2.3.4Input Shift Registers in ADF43514.2.3.5Voltage Controlled Oscillator integrated in ADF43514.2.3.6Output Stage of the ADF4351Loop FilterChecking the Stability of Phase-Locked-Loopand ADF4351 based Signal Generator | <ol> <li>29</li> <li>29</li> <li>30</li> <li>31</li> <li>32</li> <li>33</li> <li>34</li> <li>35</li> <li>36</li> <li>37</li> <li>38</li> <li>39</li> <li>40</li> </ol> |

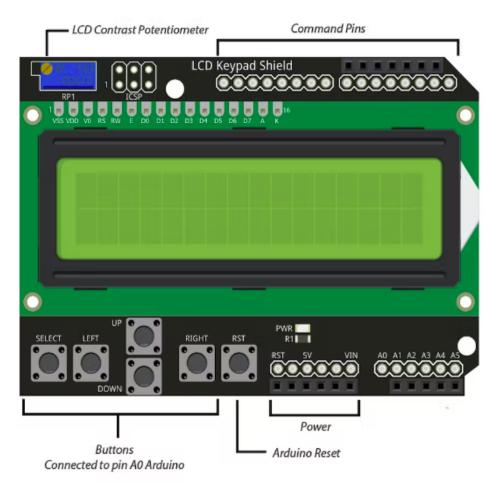

|   |     | 4.3.3            | LCD Keypad Shield                                                               | 45 |

|---|-----|------------------|---------------------------------------------------------------------------------|----|

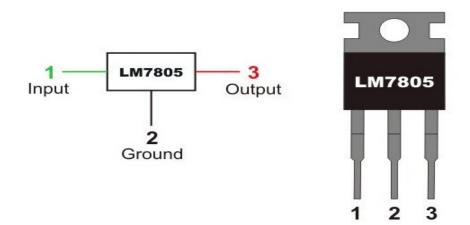

|   |     | 4.3.4            | Power Supply                                                                    | 46 |

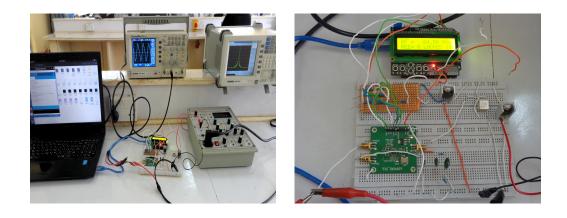

|   | 4.4 |                  | g and Measurements of the Signal Generator using Spectrum ser                   | 48 |

|   |     | 4.4.1            | GSP-830 Spectrum Analyser                                                       | 48 |

|   |     | 4.4.2            | Testing the Signal Generator                                                    | 49 |

|   |     | 4.4.3            | Measuring Phase Noise using GSP-830 Spectrum Analyser                           | 50 |

|   |     | 4.4.4            | Measuring Spurs and Harmonics using GSP-830 Spectrum Analyser                   | 51 |

| 5 | -   | APTER<br>SULTS A | FIVE<br>AND DISCUSSION                                                          | 52 |

|   | 5.1 | Introd           | uction                                                                          | 52 |

|   | 5.2 | Simula           | ation of the Phase Locked Loop                                                  | 52 |

|   |     | 5.2.1            | Reference Crystal Oscillator                                                    | 52 |

|   |     | 5.2.2            | Voltage Controlled Oscillator (VCO)                                             | 54 |

|   |     | 5.2.3            | Loop Filter Design                                                              | 55 |

|   |     |                  | 5.2.3.1 Loop Bandwidth Optimization                                             | 55 |

|   |     |                  | 5.2.3.2 Phase Margin Optimization                                               | 56 |

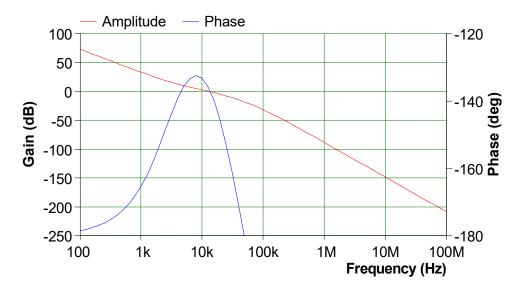

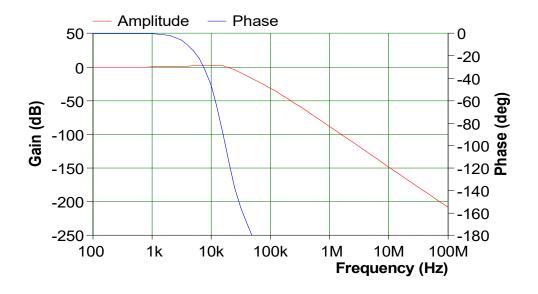

|   |     | 5.2.4            | System Behaviour                                                                | 58 |

|   |     | 5.2.5            | Output Phase Noise                                                              | 60 |

|   |     | 5.2.6            | Transient Response of Phase Locked Loop                                         | 62 |

|   |     | 5.2.7            | Checking the Stability of the PLL system Using Routh's Stabil-<br>ity Criterion | 63 |

|   | 5.3 | Impler           | mentation of the signal Generator                                               | 64 |

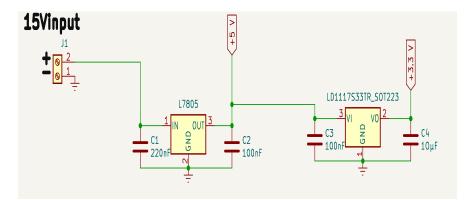

|   |     | 5.3.1            | Power supply design                                                             | 64 |

|   |     | 5.3.2            | Synthesizer Control Design                                                      | 65 |

|   |     | 5.3.3            | Keypad Shield Control                                                           | 65 |

|   | 5.4 | Tests a          | and Measurements                                                                | 66 |

|   |     | 5.4.1            | Testing the Signal Generator                                                    | 66 |

|   |     | 5.4.2            | Phase Noise Measurements                                                        | 69 |

|   |     | 5.4.3            | Spurs Measurements                                                              | 73 |

| 6 | -   | APTER<br>NCLUS   | SIX<br>HONS AND RECOMMENDATIONS                                                 | 75 |

|   | 6.1 | Introd           | uction                                                                          | 75 |

|   | 6.2 | Conclu           | usions                                                                          | 75 |

|   | 6.3 | Recon            | nmendations                                                                     | 76 |

# REFERENCES

| A | APPENDIX A<br>PYTHON SCRIPT        | 82 |

|---|------------------------------------|----|

| B | APPENDIX B<br>MICROCONTROLLER CODE | 83 |

| С | APPENDIX C<br>HARDWARE TEST SETUP  | 88 |

77

# LIST OF FIGURES

| 1.1  | Schematic representation of the primary elements comprising a fre-<br>quency synthesizer                                                    | 2  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1  | A symbol that resembles a crystal                                                                                                           | 10 |

| 3.2  | Transistor pierce crystal oscillator circuit                                                                                                | 11 |

| 3.3  | A PFD Constructed using Edge-Triggered D Flip-Flops                                                                                         | 12 |

| 3.4  | Charge pump Architecture                                                                                                                    | 13 |

| 3.5  | (a) Passive loop filter (b) Active loop filter                                                                                              | 13 |

| 3.6  | Stability analysis by Bode plot                                                                                                             | 14 |

| 3.7  | LC tank circuit                                                                                                                             | 16 |

| 3.8  | Ring oscillator                                                                                                                             | 16 |

| 3.9  | Control voltage versus output frequency                                                                                                     | 17 |

| 3.10 | Single modulus prescaler                                                                                                                    | 18 |

| 3.11 | A block diagram of a dual modulus prescaler                                                                                                 | 19 |

| 3.12 | The operation of the accumulator                                                                                                            | 20 |

| 3.13 | (a) The output that is desired from the divider (b) A sudden shift in phase resulting from the operation of a fractional divider of $1/4$   | 20 |

| 3.14 | 1st order delta sigma modulator                                                                                                             | 21 |

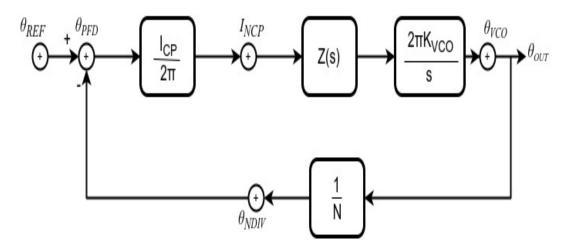

| 3.15 | A block diagram showing a Linear phase domain PLL                                                                                           | 23 |

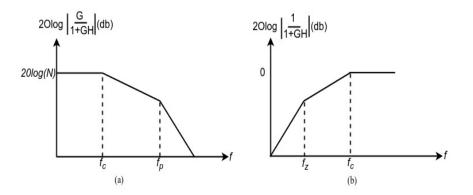

| 3.16 | Plot showing the common factor transfer function multiplying (a) the CP, the PFD, the reference, and the N divider noise (b) the VCO noise. | 24 |

| 3.17 | The basic setup of a linear regulator                                                                                                       | 27 |

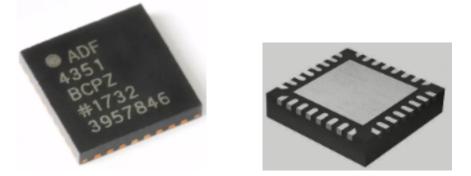

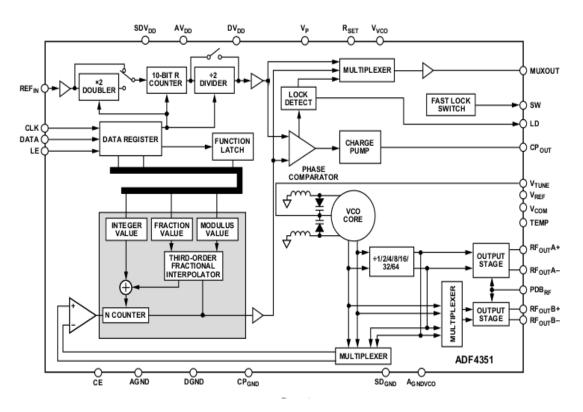

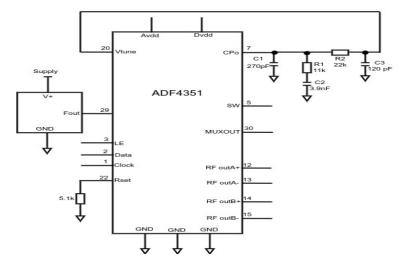

| 4.1  | ADF4351 phase locked loop chip (Devices, 2008)                                                                                              | 31 |

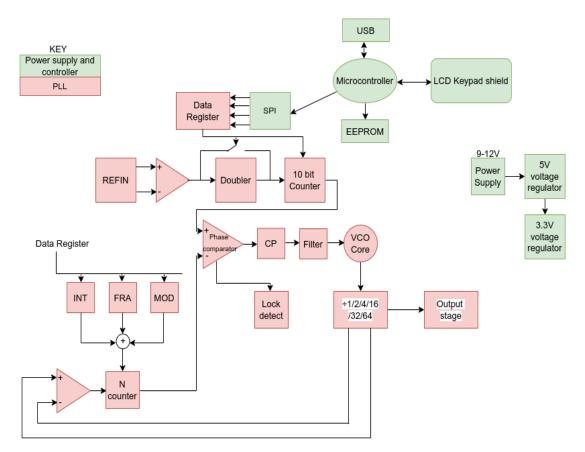

| 4.2  | An illustration of the ADF4351's functional block diagram (Devices, 2008)                                                                   | 32 |

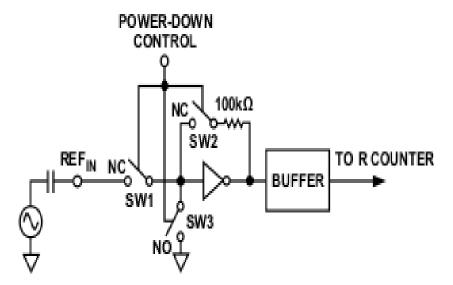

| 4.3  | Reference Input Stage in ADFF351 (Devices, 2008)                                                                                            | 33 |

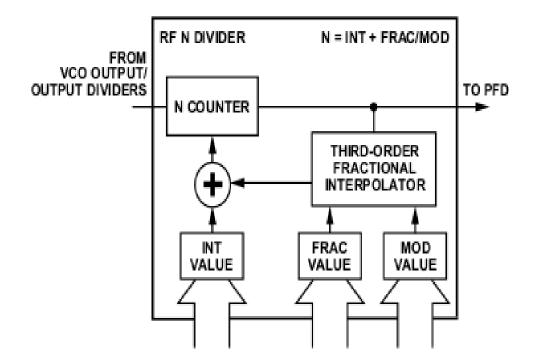

| 4.4  | ADF4351 RF N Divider (Devices, 2008)                                                                                                        | 34 |

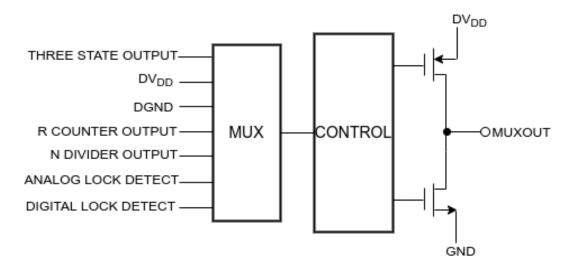

| 4.5  | Schematic diagram of multiplexer output                                                                                                     | 35 |

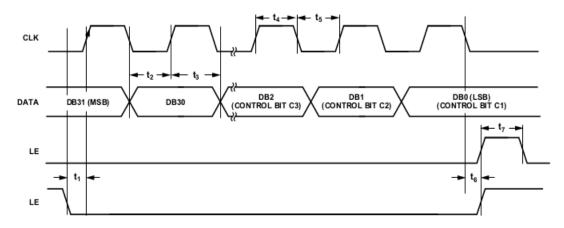

| 4.6  | Timing diagram showing how data is clocked in registers (Devices, 2008)                                                                     | 35 |

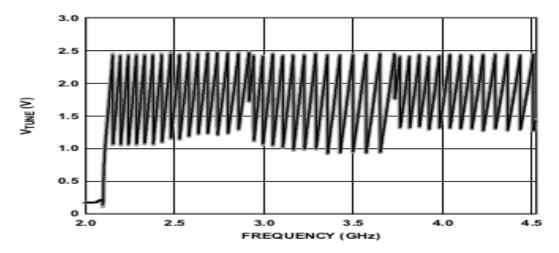

| 4.7  | Voltage- Frequency characteristics of the VCO (Devices, 2008)                                                                               | 36 |

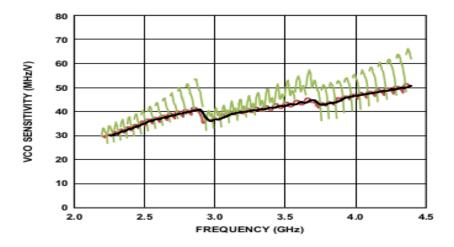

| 4.8  | VCO Sensitivity (KV) vs. Frequency (Devices, 2008)                                                                                          | 37 |

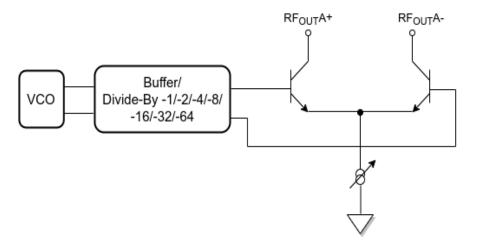

| 4.9  | Output stage of ADF4351 PLL Chip                                                                                                            | 37 |

| 4.10 | The structure of a third-order passive loop filter                                                                                          | 38 |

| 4.11 | A block diagram of PLL based signal generator                                                                                               | 41 |

|      |                                                                                                                                             |    |

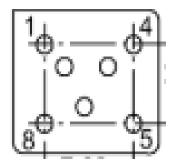

| 4.12 | 10 MHz ECS-2200X crystal oscillator (ECS, nd)                                                                           | 41 |

|------|-------------------------------------------------------------------------------------------------------------------------|----|

| 4.13 | A picture of ECS-2200X crystal oscillator pinout (ECS, nd)                                                              | 42 |

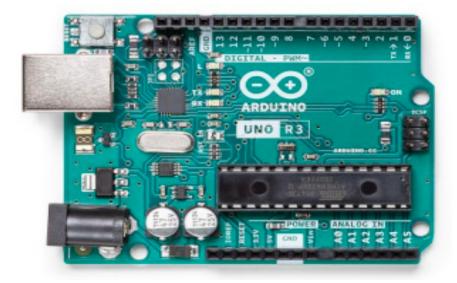

| 4.14 | The Arduino UNO board (Arduino, nd)                                                                                     | 43 |

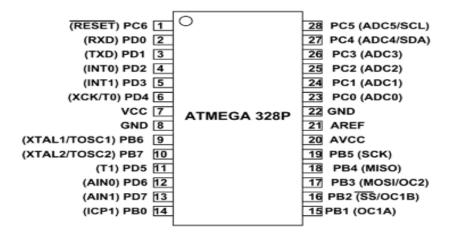

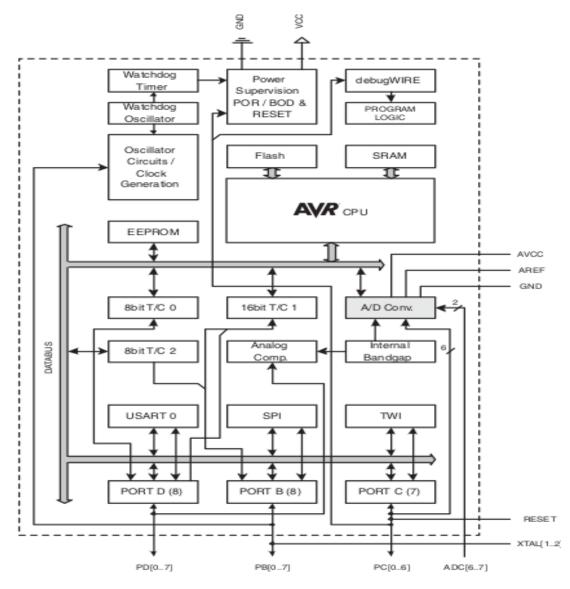

| 4.15 | Pin diagram of ATmega328P Microcontroller (Atmel, 2015)                                                                 | 43 |

| 4.16 | Block diagram of ATmega328P Microcontroller (Atmel, 2015)                                                               | 44 |

| 4.17 | LCD Keypad shield (ElectroPeak, 2019)                                                                                   | 45 |

| 4.18 | A picture of LM7805 and its pinout (Electronics, 2017)                                                                  | 47 |

| 4.19 | 4.18: A picture of LD1117aV33 (Jordan, 2010)                                                                            | 47 |

| 4.20 | A picture of GSP-830 Spectrum Analyser (Instrument, nd)                                                                 | 49 |

| 4.21 | Hardware test setup                                                                                                     | 50 |

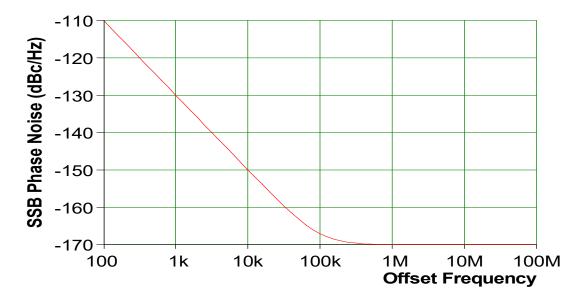

| 5.1  | The phase noise of the reference oscillator after simulation                                                            | 53 |

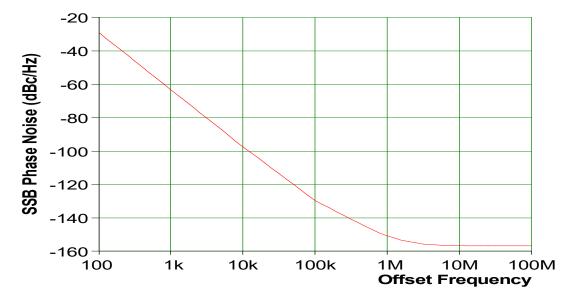

| 5.2  | phase noise performance of integrated VCO                                                                               | 54 |

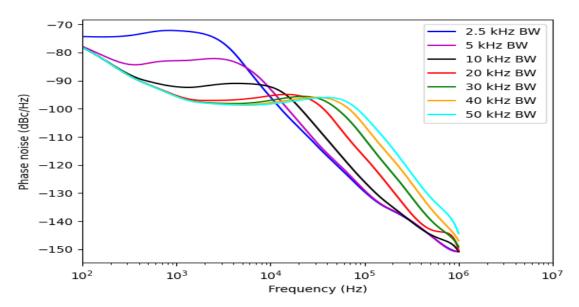

| 5.3  | Phase noise simulation for different loop bandwidths                                                                    | 56 |

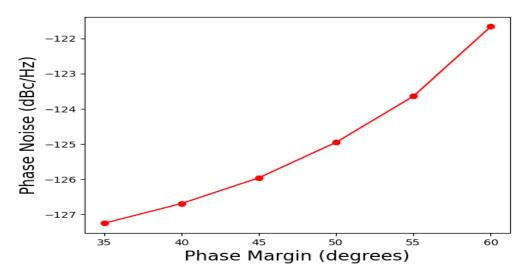

| 5.4  | Phase noise variation with respect to the phase margin                                                                  | 57 |

| 5.5  | Phase Locked Loop Schematic using ADIsimPLL                                                                             | 58 |

| 5.6  | Open loop transfer function at 387 MHz                                                                                  | 59 |

| 5.7  | The closed loop transfer function at 387 MHz                                                                            | 60 |

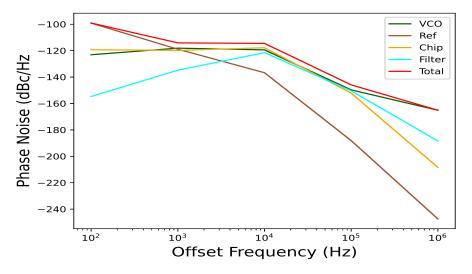

| 5.8  | The contribution of phase noise from system components and the overall response at 387 MHz                              | 61 |

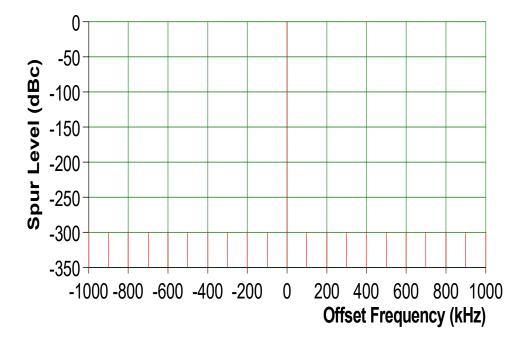

| 5.9  | Reference spurs at 387 MHz                                                                                              | 62 |

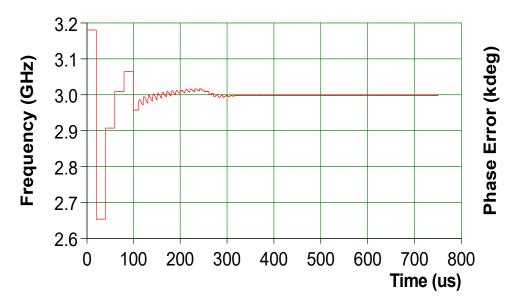

| 5.10 | Transient frequency characteristics of simulated PLL                                                                    | 63 |

| 5.11 | Circuit diagram of the power section design                                                                             | 64 |

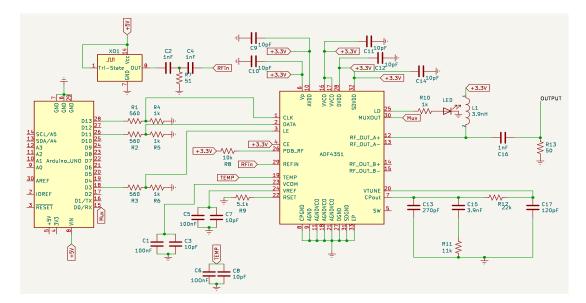

| 5.12 | Circuit diagram of the PLL chip control design                                                                          | 65 |

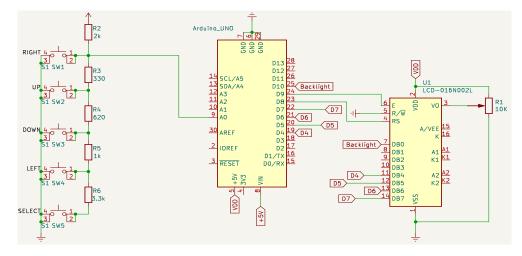

| 5.13 | Circuit diagram of the keypad shield controlled by arduino                                                              | 66 |

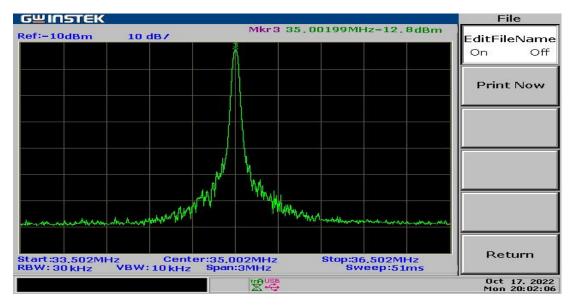

| 5.14 | Output spectrum at 35 MHz frequency on a spectrum Analyser                                                              | 66 |

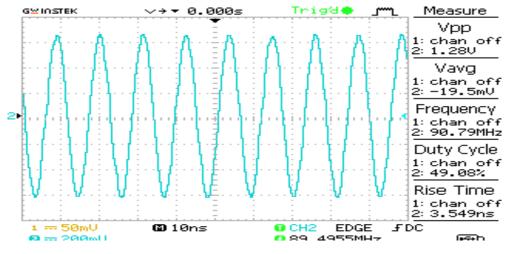

| 5.15 | Signal output from a CRO at the frequency of 35 MHz                                                                     | 67 |

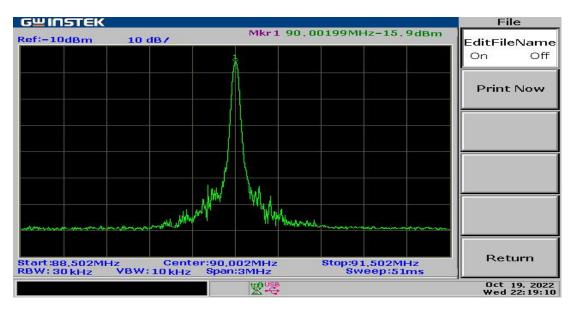

| 5.16 | Output spectrum at 90 MHz frequency on a spectrum Analyser                                                              | 67 |

| 5.17 | Output signal at 90 MHz frequency on a CRO                                                                              | 68 |

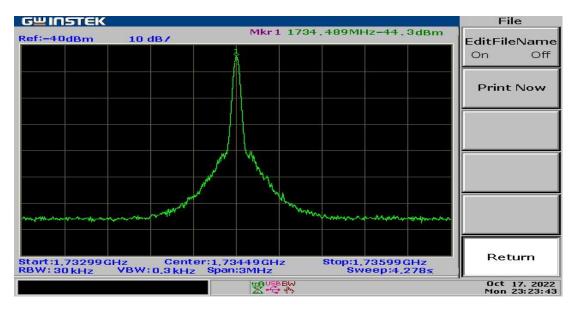

| 5.18 | Output spectrum at 1734.5 MHz frequency on a spectrum Analyser                                                          | 68 |

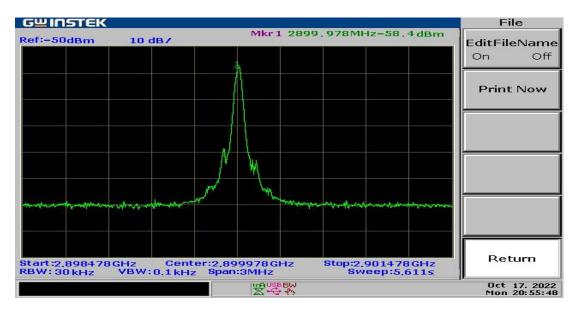

| 5.19 | Output spectrum at 2900 MHz frequency on a spectrum Analyser                                                            | 69 |

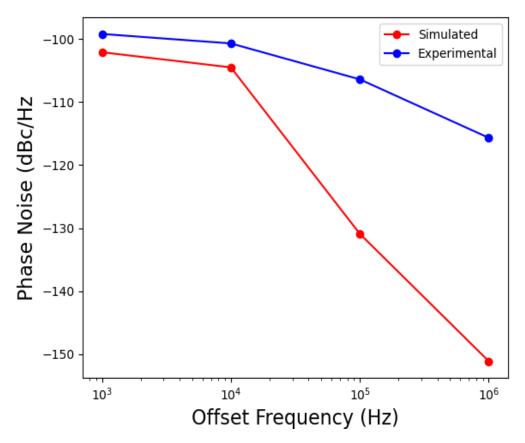

| 5.20 | A comparison of the phase noise of simulated and experimental data at 35 MHz                                            | 71 |

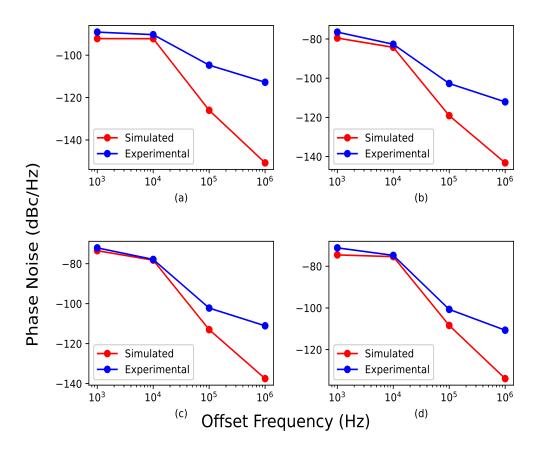

| 5.21 | A comparison of the phase noise of simulated and experimental data at (a) 387 MHz, (b) 1 GHz, (c) 2 GHz and (d) 2.9 GHz | 72 |

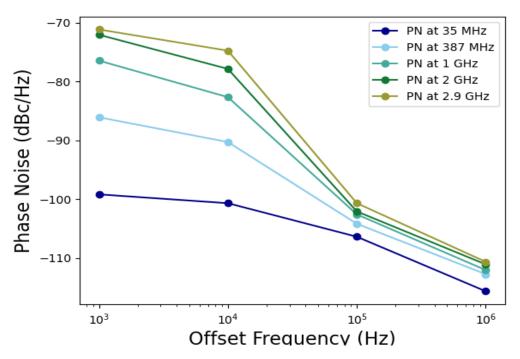

| 5.22 | Phase Noise at 35 MHz, 387 MHz, 1 GHz, 2 GHz and 2.9 GHz output frequencies                                             | 73 |

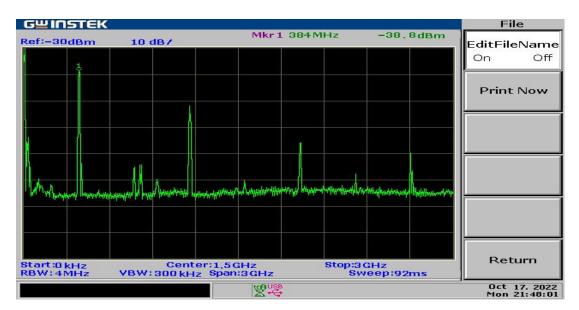

| 5.23 | Level of spurs at 387.00 MHz output frequency                                                                           | 74 |

# LIST OF TABLES

| 4.1 | PLL based signal generator non-functional requirements                                      | 30 |

|-----|---------------------------------------------------------------------------------------------|----|

| 4.2 | The truth table for the Control Bits C3, C2, and C1                                         | 36 |

| 4.3 | A Generic Routh array                                                                       | 39 |

| 4.4 | Pin connections of ECS-2200X crystal oscillator                                             | 42 |

| 4.5 | Connection of LCD Keypad shield to Arduino Pins                                             | 46 |

| 4.6 | Reading LCD Keypad Shield Keys                                                              | 46 |

| 5.1 | Phase noise of the reference crystal oscillator                                             | 53 |

| 5.2 | Specification of the voltage controlled oscillator                                          | 54 |

| 5.3 | Simulated Phase Noise and Lock Time for various Loop Bandwidths at 100 kHz offset frequency | 55 |

| 5.4 | Simulated Phase Noise for various phase margin                                              | 57 |

| 5.5 | Components of the loop filter, both optimized and standard,                                 | 58 |

| 5.6 | The Phase noise simulation results (all findings are in dBc/Hz)                             | 60 |

| 5.7 | Phase-locked loop stability according to Routh's criteria                                   | 64 |

| 5.8 | Experimental and Simulated Phase noise at 35.00 MHz, 387.00 MHz, 1 GHz, 2 GHz and 2.9 GHz   | 70 |

| 5.9 | Level of spurs at 387.00MHz output frequency                                                | 74 |

## LIST OF ABBREVIATIONS AND ACRONYMS

- AC Alternating Current

- ADC Analog to Digital Converter

- **BJT** Bipolar Junction Transistor

- **CE** Chip Enable

- CLK Clock

- CMOS Complementary Metal-Oxide-Semiconductor

- CP Charge Pump

- CPU Central Processing Unit

- CRO Cathod Ray Oscilloscope

- CSR Cycle Slip Reduction

- DAC Digital Analogue Converter

- DC Direct Current

- **DDS** Direct Digital Synthesizer

- FPGA Field Programmable Gate Array

- wosc Frequency of Oscillation

- GPS Global Positioning System

- HCMOS High Density Complimentary Metal-Oxide-Semiconductor

- **IC** Integrated Circuit

- **ICSP** In Circuit Serial Programming

- *I<sub>CP</sub>* Charge Pump Current

- **IF** Intermediate Frequency

- **ISM** Industrial Scientific and Medical

- LC Inductor Capacitor

- LCD Liquid Crystal Display

- LE Load Enable

- LFMS Linear Frequency Modulated Signal

- LPF Low Pass Filter

- LSB Less Significant Bit

- MIPS Million Instructions Per Second

- MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor

- MSB Most Significant Bit

- MUXOUT Multiplexer Output

- NMOS N channel Metal-Oxide-Semiconductor

- PC Personal Computer

- **PFD** Phase Frequency Detector

- PLL Phase Locked Loop

- PMOS P channel Metal-Oxide-Semiconductor

- ppm parts per million

- **RADAR** Radio Detecting and Ranging

- **RBW** Resolution Bandwidth

- **RC** Resistor Capacitor

## **RFB** Feedback Resistors

- **RFC** Radio Frequency Choke

- **RISC** Reduced Instruction Set Computer

- SFCW Step Frequency Continuous Waves

- $T_{SW}$  Switching Speed

- TTL Transistor-Transistor Logic

- **USB** Universal Serial Bus

- **VBW** Video Bandwidth

- VCO Voltage Controlled Oscillator

- VCXO Voltage Controlled Crystal Oscillator

- VFB Feedback Voltage

- **VREF** Reference Voltage

- Wi-Fi Wireless Fidelity

- WIMAX Wireless Inter-operability for Microwave Access

#### ABSTRACT

A signal generator is an electronic test instrument that has a wide range of applications. Some of these applications include testing systems in cellular communications, radar, microstrip antennas and testing components in electronics labs. For a signal generator to be used in these applications, it should generate high frequencies, have a low level of phase noise, and also have a fast locking time. The purpose of this research was to design and build a signal generator that operates on the principle of a phase-locked loop, has the capacity to generate frequencies ranging from 35 MHz to 3 GHz, and has a low degree of phase noise. The simulation of the phase-locked loop synthesizer was done using the ADIsimPLL design tool. The phase locked loop chip used in simulation was the ADF4351 from Analog Devices. In the design, we implemented a loop filter of the third order and chose a reference frequency of 10 MHz. The layout of the phase locked loop was simulated, and the results showed that the optimal values for loop bandwidth and phase margin were 10 kHz and 45°, respectively. Following the simulation, the optimal values for each of the loop filter's components were analyzed and calculated. The signal generator was built by integrating the phase locked loop synthesizer and a keypad shield with an Arduino UNO microcontroller. The ADF4351 was programmed via Serial Peripheral Interface (SPI) to enable the changing of frequencies using the keypad shield. The nature of the generator's signal was investigated using a cathode ray oscilloscope in the 35-100 MHz frequency range. The testing was also done for 101-3000 MHz using a spectrum analyser. The level of phase noise was calculated at 35 megahertz, 387 megahertz, 1 gigahertz, 2 gigahertz, and 2.9 gigahertz at 1, 10, 100, and 1000 kilohertz. The amount of phase noise that was acquired after experimental work was higher than the level obtained after simulation. For example, at the output frequency of 387 MHz, the experimental phase noise was -104.2 dBc/Hz while the simulated was -126 dBc/Hz at 100 kHz offset frequency. The reason for this is that the phase noise contribution in the simulation was only from the phase locked loop components while in the experimental, in addition to the phase noise from the PLL components, there were other sources of phase noise while carrying out the experiment. The rise in output frequency was also accompanied by an increase in phase noise. The reason for this is that the signal generator was built with the concept of a phase locked loop which implements the idea of frequency multiplication by dividing along the feedback loop with the use of a counter. This concept raised the phase noise by 20 multiplied by the logarithm of the number of counter. The maximum spur appeared at the third harmonic and was found to be -18.6 dBc, while the minimum spur appeared at the fourth harmonic and was found to be -44.5 dBc.

## **CHAPTER ONE**

#### **INTRODUCTION**

This chapter gives background information on the research subject. It also provides the statement of the research problem, its rationale and research objectives.

#### **1.1 Background of the Study**

A signal generator is an instrument that produces waveforms that are either repeating or non-repeating and can be used in testing electronics devices (Qi *et al.*, 2015). In a laboratory for electronics and in experimental courses, this device can be used for a broad variety of tasks, such as characterizing digital and analog systems (Muteithia, 2014). Numerous methods can be used for generating waveforms in signal generators. These methods include the resistor-capacitor (RC) oscillator, direct digital synthesizers (DDS), inductor-capacitor (LC) oscillator, crystal oscillator, Phase Locked Loop (PLL) synthesizers, as well as various variants of these technologies (Vankka, 2000).

For this study, a frequency synthesizer based on PLL was used to generate frequencies. This is due to the fact that PLL generates frequencies with a wide output range, a low level of phase noise, high accuracy and a fast locking period when designed well (HOSSEINI and Masoumi, 2017).

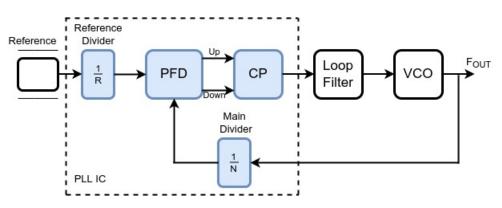

A frequency synthesizer is an electrical circuit that can generate a broad range of frequencies from a single frequency source (Fox, 2002). When a frequency synthesizer uses PLL technology to generate its output, it is called an indirect frequency synthesiser. A PLL is a control circuit with feedback that is frequency or phase-sensitive and synchronizes the output signal of the Voltage Controlled Oscillator (VCO) with a reference signal (Shurender *et al.*, 2013). PLL synthesizers are commonly used in communication systems in wireless transmission because they have excellent frequency resolution and their ability to lock quickly in time(Patel and Sharma, 2010). Figure 1.1 shows the main components of a PLL, which include a phase or frequency detector

(PFD), filter, Charge Pump (CP), feedback divider (1/N) and VCO (del Rocío Ricardez-Trejo *et al.*, 2017).

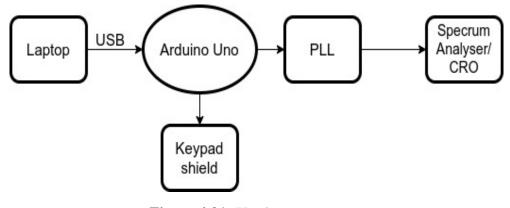

**Figure 1.1:** Schematic representation of the primary elements comprising a frequency synthesizer

A comparison is made by the phase or frequency detector, between the frequency from the reference signal and the frequency that is generated by the VCO. It creates two output signals, "UP" and "DOWN," depending on the deviation of the phase. The CP combines the signals generated by the PFD and provides an output. This output is then sent on to the low pass filter so that spurs generated by the PFD can be reduced. The CP also changes the signal from a phase or frequency state to a voltage state, which is used to vary the VCO. When the phase of the two signals has a difference of zero, the system is said to be locked.

A signal is sent out by the VCO, the nature of which is determined by the voltage that the CP produces. When the signal at the output of the PFD is outrageous, the voltage output of the CP component rises, which in turn causes an increase in the output frequency of the VCO. Similarly, the output of the VCO drops if there is a low level of PFD output. After that, the frequency that the VCO generated is sent to the PFD to recalculate the fluctuation in phase, which ultimately results in the creation of a locked-loop frequency control system (Barret, 1999). For the phase locked loop to generate high frequencies and of wide range, the concept of frequency multiplication is carried out by using an N counter to divide along the feedback loop. Equation 1.1 can be used to calculate the output frequency of the system.

$$F_{OUT} = N \times F_{REF} \tag{1.1}$$

where,  $F_{OUT}$  is the frequency at which the VCO produces its output, N is a feedback division ratio, and  $F_{REF}$  is the frequency at which the reference produces its output

It is possible to adjust the divider so that the division ratio, N, takes the form of either a whole number or a fraction (Mutinda *et al.*, 2023). This can result in a PLL with either an integer value of N or a fractional value of N (Harney, 2009). An integer N-PLL synthesizer's resolution relies on a reference frequency to function properly. As a result, the reference frequency is divided down by R to obtain a high-frequency resolution, which results in the frequency resolution shown in equation 1.2.

$$F_R = \frac{F_{REF}}{R} \tag{1.2}$$

where,  $F_R$  represents the frequency resolution,  $F_{REF}$  stands for the frequency of reference, and R stands for the division ratio for reference.

Following this, the frequency at which the signal is produced can be calculated using equation 1.3.

$$F_{OUT} = \frac{N}{R} F_{REF} \tag{1.3}$$

A significant amount of phase noise is typically present in the signals produced by an integer N-PLL. This is due to the fact that, in accordance with the frequency multiplication principle, there is an increase of 20log(N) dB in the phase noise of the signal (Barret, 1999). The resolution in a fractional N-PLL which is a fractional part of the resulting frequency produced by the phase detector is attained. This is made possible by an inner circuitry that allows the magnitude of N to vary incrementally when the PLL is in lock condition. When the divider is switched between two consecutive values in the correct division, an ordinary division ratio is realized as N and an arbitrary function y/z.

The frequency of the output is calculated using equation 1.4.

$$F_{OUT} = F_{REF} \left( N + \frac{Y}{Z} \right) \tag{1.4}$$

where, N, Y and Z are integers, N is the feedback partition ratio, Y is the value of fraction register and Z is the value of modulus register (Barret, 1999).

#### **1.2** Statement of the Problem

As time goes on, the number of applications that use microwave signals, such as mobile communication, satellite communication, radar, microstrip antennas and Wi-Fi, continues to grow. Therefore, there is a need to design and implement a high frequency signal generator with a low level of phase noise (<100 dBc/Hz), a fast locking time ( $\leq 1$  ms) and the ability to generate frequencies up to the microwave range.

The goal of this work was to create a PLL-based signal generator that can generate frequencies in the 35 MHz–3 GHz range to be used in testing devices operating in this frequency range.

#### 1.3 Justification of the Study

In this research, the signal generator was designed using the concept of PLL. This is because phase-locked loop (PLL) synthesizers generate stable and clean signals. They also produce frequencies that have a wide output range compared to frequencies generated using the DDS concept. PLL also has a fast locking time and provides a good platform for the implementation of a signal generator in terms of performance and power consumption.

## 1.4 Objectives

## **1.4.1 General Objective**

The primary aim of this research was to design and implement a phase locked loop based signal generator which can generate frequencies in the range of 35 MHz–3 GHz.

### 1.4.2 Specific Objectives

- i. To simulate and design a PLL synthesizer, reference frequency, low pass filter, and VCO using the ADIsimPLL design software.

- ii. To build a high frequency signal generator following the results obtained after simulation.

- iii. To test the functioning of the signal generator.

- iv. To carry out measurements and analysis of phase noise and spurs.

#### 1.5 Significance of the Study

This study aimed at designing a signal generator that could output frequencies in the microwave range. This signal generator can be applied in many areas, such as testing components in electronics laboratories, characterization of microstrip antennas and testing systems in a wide variety of applications, which include Wireless Fidelity (Wi-Fi)and Wireless Inter-operability for Microwave Access (WiMAX). Signal generators can help in assessing the performance of satellite ground station receivers. It can also be used in broadcast transmitters and receivers and in testing system in Global Positioning System (GPS).

## **CHAPTER TWO**

#### LITERATURE REVIEW

#### 2.1 Introduction

This chapter provides an overview of the earlier studies that were conducted on direct digital synthesis and phase locked loop based signal generators. Various simulation tools that have been used in designing phase lock loop system are also discussed in this chapter.

#### 2.2 Direct Digital Synthesis based Signal Generators

Li *et al.* (2012) proposed an l-band synthesizer system with high agility and large bandwidth using a direct digital synthesis (DDS) and a scheme of frequency multiplication. Their proposed synthesizer first produces a baseband linear frequency modulated signal (LFMS) using DDS, and then the signal produced is added to a frequency multiplication system that can transform the baseband signal into 1-band LFMS with a range of 1424 MHz-1950 MHz, which is quite low.

Bonfanti *et al.* (2003) presented a PLL based on DDS, that had an output frequency of 2.4 GHz with an 80-MHz tuning range. Their design achieved a high-frequency resolution of 1 kHz, a fast switching time of 3 µs and spectral purity of -50 dBc. The main weakness of this device was the high power consumption of the DDS-DAC blocks.

Du *et al.* (2017) presented a field programmable gate array (FPGA) and DDS based signal generator. The FPGA was used to provide the settling period order for the DDS. They obtained a 1.4 gigahertz frequency with a good resolution of approximately 190 picohertz. The level of phase noise calculate at a 1.2 gigahertz was found to be -65 dBc/Hz at a 1 Hz offset frequency, and a settling time of 150 ns was also obtained.

#### 2.3 Phase Locked Loop Generators

Hwang *et al.* (2000) proposed a digitally controlled PLL to be applied in clock synthesis. Their design achieved a fast clock time and a frequency range of 300 MHz-800 MHz, but due to the resolution limitation of the DAC and the low sensitivity of the frequency detector, its jitter was very high, 149 ps p-p. Yang *et al.* (2012) designed an ultra-broadband frequency synthesizer that had a high resolution and low power consumption. In their design, DDS was used as the reference for the broadband PLL. Using their approach, they were able to obtain broadband ranging from 137.5 MHz to 4.4 GHz with 128 µHz resolution. However, this approach is costly because it requires many components. Shurender *et al.* (2013) designed a PLL-based indirect frequency synthesis for the s band frequency. They minimized spurious signals by narrowing the bandwidth of the filter. However, this resulted in a longer lock time.

Handique and Bezboruah (2015) designed and analysed a PLL based synthesizer operating in the range of 128 to 256 megahertz which can be applied in communication systems that are wireless. They recorded phase noise of -80.9 dBc/Hz and -107.8 dBc/Hz at an offset frequency of 10 and 1000 kilohertz, respectively. Fajar *et al.* (2019) designed a fractional based signal generator for detecting a high-resolution object or subsoil structure. They used an ADF4351 synthesizer, which was controlled by a microcontroller. Their signal generator generated output signals in the range of 0.5 GHz - 1.5 GHz.

Kameche and Feham (2013) designed and simulated an integer-N frequency synthesizer for exchanging data over short distances, operating in 2400 MHz–2480 MHz range with a 1 MHz frequency step. This design had a switching time of about 50.83  $\mu$ s. Despite this, the design resulted in a phase noise of -82 dBc/Hz when the offset was adjusted to 1 MHz, which is an extremely high value. Rout *et al.* (2014) performed an analysis and developed a 1 GHz PLL in order to achieve rapid acquisition of phase and frequency.

They discovered that the PLL settling time was largely determined by the type of PFD design that was utilized, in addition to the charge pump and the loop filter. They were able to accomplish a lock time of 280.6 ns at a frequency of 1 GHz by making the appropriate choices for these parameters. Kumar and Shrimali (2022) constructed a subcutaneous medical device that uses a frequency synthesizer based on a phase-locked loop of the second order for monitoring and performing medical diagnoses in a human body. The weakness of their design was that it had only one output frequency of 450 MHz.

### 2.4 Simulation of PLL

Sun (2013) did research on designing and debugging a phase locked loop synthesizer. He recommended that designers of PLL based synthesizer use the ADIsimPLL tool software for simulation. Shurender *et al.* (2013) designed an S-band frequency synthesizer for microwave applications using fractional-N PLL. They used ADIsimPLL software to simulate and design PLL. They also simulated the total phase noise contributed by PFD, filter and the VCO.

del Rocío Ricardez-Trejo *et al.* (2017) implemented a Matlab -based PLL simulator for modeling and simulating blocks of PLL based microwave generators. Telba *et al.* (2004) described Matlab Simulink simulation method for noise and jitter in PLL. They studied two methods of reducing jitter, either by using a PLL that has a small band filter or with a narrow voltage controlled crystal oscillator (VCXO) by simulation using Matlab Simulink.

HOSSEINI and Masoumi (2017) designed and implemented an ultra-high band and high precision synthesizer. They simulated the system with the ADIsimpPLL software so that they could calculate the level of phase noise and the settling period. They also applied the simulation to realizing and avoiding mistakes that occur during designing. According to the previous research, many challenges result when designing a PLL to operate at high frequencies. The goal of this study was to identify the lowest value of phase noise that could be achieved. By calculating the ideal value of the loop bandwidth for the filter that was going to be implemented in the system, the phase noise was brought down significantly. After running simulations of the PLL synthesizer with a number of different loop bandwidths, the optimal loop bandwidth that produced the lowest level of phase noise was chosen.

## **CHAPTER THREE**

#### THEORETICAL BACKGROUND

#### 3.1 Introduction

This section offers an overview of the theoretical underpinnings of the primary components of the signal generator that is built on a PLL. Under the context of a phase lock loop system, this chapter further delves into phase noise and the degree of spurs.

#### 3.2 Components of a Phase Locked Loop

#### 3.2.1 Reference Crystal Oscillator

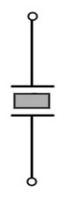

A reference crystal oscillator should have high frequency stability. For this reason, quartz crystals are used since they can overcome some factors that affect an oscillator's stability, such as variations in temperature, load and DC power supply. Piezoelectric effect is the ability of a crystal to generate an electrical charge in reaction to applied mechanical force, and it is reversible. This effect is utilized by Quartz Crystal Oscillators, and it is what allows them to produce oscillations. For the crystal to function properly in an electronic circuit, it is given the form of a capacitor by being sandwiched in the middle of two metal plates. Figure 3.1 illustrates the symbol of a crystal oscillator.

Figure 3.1: A symbol that resembles a crystal

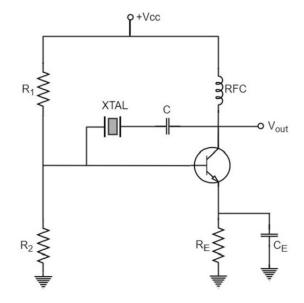

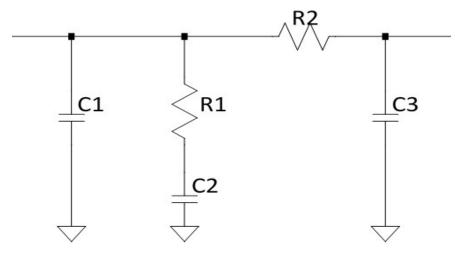

The most commonly used crystal oscillator circuit is the transistor pierce crystal oscillator, which is shown in Figure 3.2. The connections of resistors  $R_1$ ,  $R_2$ , and  $R_E$  work together to form a voltage-divider which outputs a stable signal. The capacitor  $C_E$  is what enables the AC bypass for the emitter resistor. The Radio Frequency Choke (RFC) coil is what generates the DC bias and also decouples AC signal that may be present on the power lines from having an effect on the output signal. The coupling capacitor C eliminates any DC current that might flow between the collector and the base.

Figure 3.2: Transistor pierce crystal oscillator circuit

The term "stability" refers to the oscillator's capacity to keep the frequency of its output signal unchanged over a considerable period of time. The stability is usually expressed in parts per million (ppm) which can be represented in the form of frequency as shown in equation 3.1 (Lacoste, 2014).

$$Variation in Hz = \frac{f \times ppm}{10^6}$$

(3.1)

where, f is the central frequency, which is measured in hertz (Hz), and ppm is the frequency variation, which is measured in parts per million.

## **3.2.2** Phase / Frequency Detector (PFD)

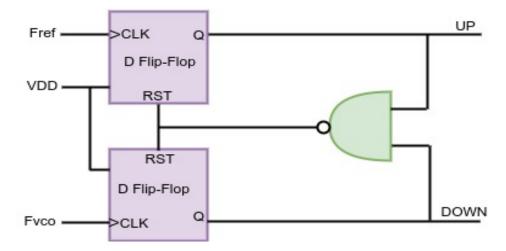

Memory components such as flip-flops are utilized in the construction of the tri-state PFD, which is the commonly used phase detector. An edge-triggered PFD that is

made up of two D flip-flops and a NAND gate in the reset path is shown in Figure 3.3 (Debnath, 2015). The undetected phase difference range, sometimes known as dead zones, is decreased when the reset path contains a delay element.

Figure 3.3: A PFD Constructed using Edge-Triggered D Flip-Flops

When the reference signal is ahead of the phase of the VCO output, the PFD will provide an "Up" error signal. In a similar fashion, a "Down" error signal is produced whenever the VCO output is ahead of the reference signal.

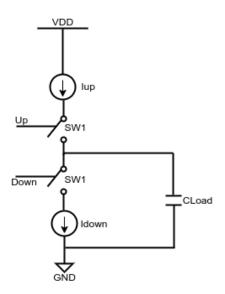

#### 3.2.3 Charge Pump

To produce the current signal Icp, which is equivalent to the phase error signal generated by the PFD, the charge pump is utilized in conjunction with the PFD. Figure 3.4 depicts a diagrammatic representation of a fundamental charge pump. A charge pump consists of two switches, and the "Up" and "Down" pulses on the PFD are the ones that control those switches. When the "Up" signal is high and the "Down" signal is low, switch SW1 is active, switch SW2 is disabled, and a current called IUp flows through the load capacitance. This charges the capacitance to the supply voltage. On the other hand, when the "Down" signal is high, current IDown is sunk, which ultimately results in the load capacitor being discharged. If "Up" and "Down" signals are both high, the current is sourced and sinked equally, and if low, the switches are turned off, and in both cases, there is no current in the load (Behzad, 2012).

Figure 3.4: Charge pump Architecture

## 3.2.4 Loop Filter

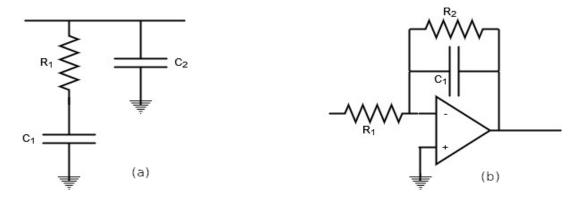

It is the job of the filter to remove the phase inaccuracy and the disruption introduced by the higher frequency terms from the output of the PFD. There is flexibility in the design of the filter, which can either be active or passive, as shown in Figure 3.5. Active filters were mostly used in old fashioned PLLs in order to improve the lock in ranges and help match the voltage swings of the PFD with the VCO. Because there are no lock-in range issues in modern PLLs that are integrated with charge pumps, passive filters are the best option. Because of how the new PLL designs are constructed, active filters are no longer required. This is due to the fact that active devices raise both the cost and the complexity of the system(Banerjee, 2017).

Figure 3.5: (a) Passive loop filter (b) Active loop filter

When designing a loop filter, it is essential to select the appropriate filter architecture, phase margin, filter order, and loop bandwidth. We get to know the order of the loop filter by determining the number of poles. Raising the order of the filter will improve the attenuation response of the filter, which will help in the filtering of spurs. Adding more components raises the order, but each of those components has their own thermal noise, which adds to the overall phase noise. The order should be carefully selected because using higher orders may reduce the phase margin at unity gain, which causes instability.

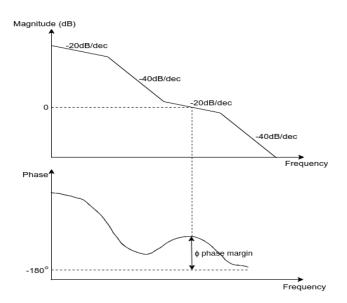

Instability is checked by analyzing the bode plot of the system. Figure 3.6 shows a sample bode plot. At unity gain frequency, the difference between the phase of the loop gain and -180 degrees is referred to as the phase margin. When the phase margin is increased too much, the lock time is lengthened; nevertheless, the instability increases when the phase margin is decreased too much. Phase margin is generally chosen between  $40^{\circ}$  and  $55^{\circ}$  (Banerjee, 2017).

Figure 3.6: Stability analysis by Bode plot

The open loop transfer function of a second-order filter has one zero and two poles, which means that the filter is always stable. When applied to very far apart frequencies, a pole and a zero will produce phase shifts of -90 degrees and 90 degrees, respectively.

This indicates that the phase margin can never be 0 if they are positioned in the appropriate locations, which makes the loop stable. It is possible that the phase shift will be more than -180 degrees at unity if the order is raised, as this will result in the addition of new poles. This results in the beginning of oscillations that are not desired. Therefore, it is important to carefully place the poles and zeros of higher order filters to avoid causing instability.

Another crucial element that contributes to the overall performance of the PLL is the loop bandwidth, which is the point at which the output signal is reduced to -3 dB relative to the input signal. The relationship between bandwidth and the switching speed is given by equation 3.2.

$$T_{SW} \propto \frac{1}{\omega_n \xi}$$

(3.2)

where  $\omega n$  is the loop bandwidth,  $T_{SW}$  is the switching speed, and  $\xi$  is the damping factor.

As a result, a reduction in bandwidth causes the system to lock up for an extended period of time and also results in an increase in the attenuation of spurs.

#### 3.2.5 Voltage Controlled Oscillator

It generates a stable output frequency from a reference that operates at a significantly lower frequency. The most common forms of oscillators found on integrated circuits are ring oscillators and LC-tuned oscillators.

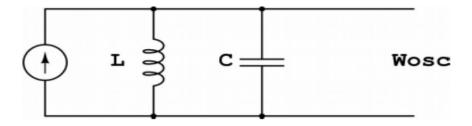

LC- tuned oscillators have a satisfying level of phase noise at gigahertz frequencies (Yoon, 2004). As can be seen in Figure 3.7, they are made up of inductors and capacitors that are connected in parallel to a current source in order to produce an LC tank circuit, which is also referred to as an LC resonator circuit. If it is designed appropriately, the

tank should be able to produce the desired output oscillation. Equation 3.3 is what decides how much oscillation there is in the output.

$$w_{osc} = \frac{1}{\sqrt{LC}} \tag{3.3}$$

where, w<sub>OSC</sub> is the frequency of oscillation, LC is the Inductance-Capacitance

Figure 3.7: LC tank circuit

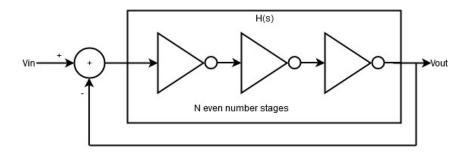

A ring oscillator is known to be a good power consumer, and they also have large tuning ranges. However, they have poor phase noise in the gigahertz frequency range in comparison to the LC-tuned oscillators. As can be seen in Figure 3.8, they are usually constructed using an odd number of delay stages.

Figure 3.8: Ring oscillator

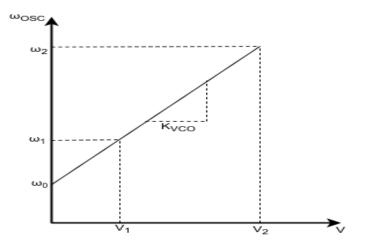

The gain of the voltage controlled oscillator (KVCO) is the extent to which the output frequency of the VCO changes for a change in input voltage, and the units are expressed in MHz/V. A fundamental plot of control voltage vs frequency of oscillation is shown in Figure 3.9, and this plot is used to determine the VCO gain. The VCO gain, or sensitivity, is determined by equation 3.4.

$$K_{VCO} = \frac{\omega_2 - \omega_1}{V_2 - V_1} \tag{3.4}$$

where,  $\omega_2$  and  $\omega_1$  is the final and initial voltage respectively, and  $V_2$  and  $V_1$  is the final and initial voltage respectively

Figure 3.9: Control voltage versus output frequency

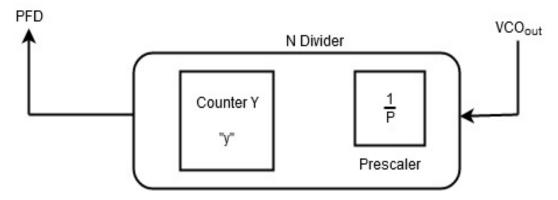

## 3.2.6 Programmable Frequency Divider

A frequency divider can be defined as any system that is capable of dividing an output frequency by a certain number. Digital counters, which are manufactured using low frequency processes such as CMOS, are utilized as divisions for VCO frequencies that are lower than 200 MHz. Because a pure CMOS counter cannot function at higher frequencies, prescalers, which are fixed higher frequency dividers, are utilized to bring the frequency of the VCO down to a range that is more amenable to use by the counters (Bölücek, 2009).

Figure 3.10 depicts a single modulus prescaler, which includes both a fixed value prescaler and a counter. The value of the prescaler is set to P, and the counter has been programmed to read "y". Equation 3.5 provides the division rate, which can be altered by making adjustments to the value of y in the counter. One of the limitations of this divider is that the division ratio can only be determined using integer multiples of P

(Bölücek, 2009).

$$N = y \times p \tag{3.5}$$

where N is the total divider value, y is the Y counter value and p is the prescaler value.

Figure 3.10: Single modulus prescaler

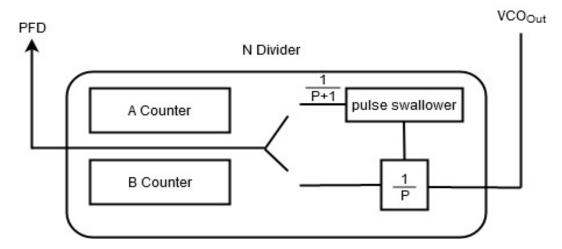

Dual modulus prescalers on the other hand are designed to increase the resolution of the division. The design utilizes just one prescaler with the size P and a value of P+1. This value is achieved by inserting a pulse swallow function directly in front of the prescaler, as demonstrated in Figure 3.11. The A counter and the B counter begin counting at the same precise moment. The pulse swallow function is disengaged once the P+1 prescaler has completed its "a" cycles of operation and the A counter has reached zero. The B counter, which has a prescaler value of P, keeps counting for b-a cycles. The division ratio is calculated as shown in equation 3.6. A limitation that states b value must be higher than or equal to "a" value must be satisfied for the operation to be carried out correctly. In the event that this requirement is not fulfilled and the incorrect N value is reached, the counter will prematurely reset before the A value hits zero (Bölücek, 2009).

$$N = a(P+1) + P(b-a) = Pb + a$$

(3.6)

where, N is the total divider value, a is number of cycles for A counter, b is the

number of cycles for B counter, P is the prescaler value.

Figure 3.11: A block diagram of a dual modulus prescaler

### 3.3 Fractional-N Phase Locked Loop

The calculations and the working of fractional-N PLLs are similar to those of integer N PLLs. The only time a distinction is made is during the process of putting the mechanism for division into action. This is due to the fact that fractional division must be obtained through the dynamic switching between at least two integer values. There are no devices available that can divide by fractional values. When we divide the total number of F cycles by N+1 for K times and by N for F-K times, the result is a fraction, which can be shown in equation 3.7 (Barret, 1999).

$$N_T = \frac{K(N+1) + N(F-K)}{F} = N + \frac{K}{F}$$

(3.7)

where  $N_T$  is the total divider value, N is the feedback division ratio, K is the fraction register and F is the modulus register.

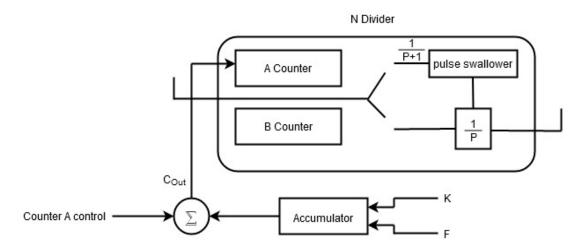

The fractional-N PLL is integrated with a fractional accumulator, as shown in Figure 3.12, which changes the N value dynamically when the PLL is locked. When the accumulator reaches its maximum capacity, the carry out is activated, and the value of the A counter is increased by one. The value of F indicates the number of reference cycles that are contained within each complete fractional divide cycle. On the other

hand, the value of K indicates the number of times the device will divide by N+1 during each full fractional divide cycle. In the event that we take into consideration a dual modulus divider, for every K times during F cycles, if a is increased by one, then N is likewise increased by one (Barret, 1999).

Figure 3.12: The operation of the accumulator

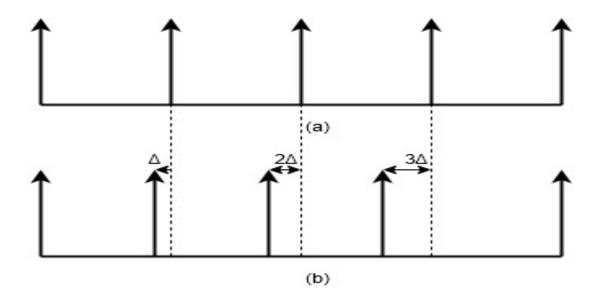

When N is incremented by 1, it causes an abrupt change in phase on a periodic basis, as shown in Figure 3.13, which leads to a spurious signal known as a fractional spur. These spurs fall into the loop bandwidth since their frequencies are low, and they cause poor working of the synthesizer if not eliminated.

**Figure 3.13:** (a) The output that is desired from the divider (b) A sudden shift in phase resulting from the operation of a fractional divider of 1/4

Fractional spurs can be minimized by using analog techniques, such as current compensation in the loop filter and the introduction of phase delay at the phase detector, but it is not an efficient method. The efficient method to minimise fractional spurs is to use delta sigma ( $\Sigma$ - $\Delta$ ) modulators in the PLL, which make compensation in the digital domain (Banerjee, 2017).

#### **3.3.1** Delta Sigma ( $\Sigma$ - $\Delta$ ) Modulators in Fractional Phase Locked Loop

Switching between two integer values and calculating the average of those values in order to arrive at a fractional value is the fundamental logic that underpins the operation of fractional N synthesizers, as was mentioned earlier. The switching between two integers is actually a first order  $\Sigma$ - $\Delta$  modulator although not common. In the vast majority of instances,  $\Sigma$ - $\Delta$  modulators begin with the second order, which toggles in and out of four integer values. In a nutshell, the output of an nth order  $\Sigma$ - $\Delta$  modulator jumps back and forth between  $2^n$  integers.

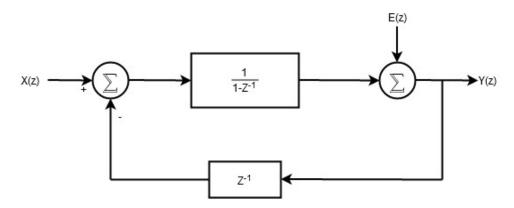

The fractional spurs are improved with this design by increasing the number of division rates, which gets rid of the sudden phase change that generates the spurs in the first place. Increasing the division rate also pushes the fractional spurs caused by the divider to a higher frequency, enabling the loop filter to eliminate them easily (Bölücek, 2009). The first order delta sigma is modelled using a quantization noise or quantization error E(z) which is added to a divider as shown in Figure 3.14.

Figure 3.14: 1st order delta sigma modulator

Equation 3.8 determine the transfer function of the system depicted in figure 3.14.

$$Y(z) = X(z) + E(z)(1 - Z^{-1})$$

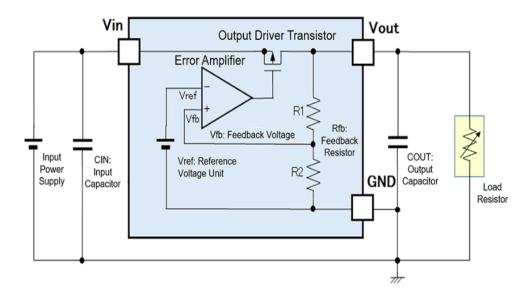

(3.8)